# Enhancing the Role of Latin America in the Semiconductor Global Value Chain – Part 2: Supply Chain Dynamics

Preparado por: Jeancarlos Chen y Jorge Barnett

Centro de Innovación e Investigaciones Logísticas Georgia Tech Panamá

Agosto, 2023

# Enhancing the Role of Latin America in the Semiconductor Global Value Chain

Part 2: Supply Chain Dynamics

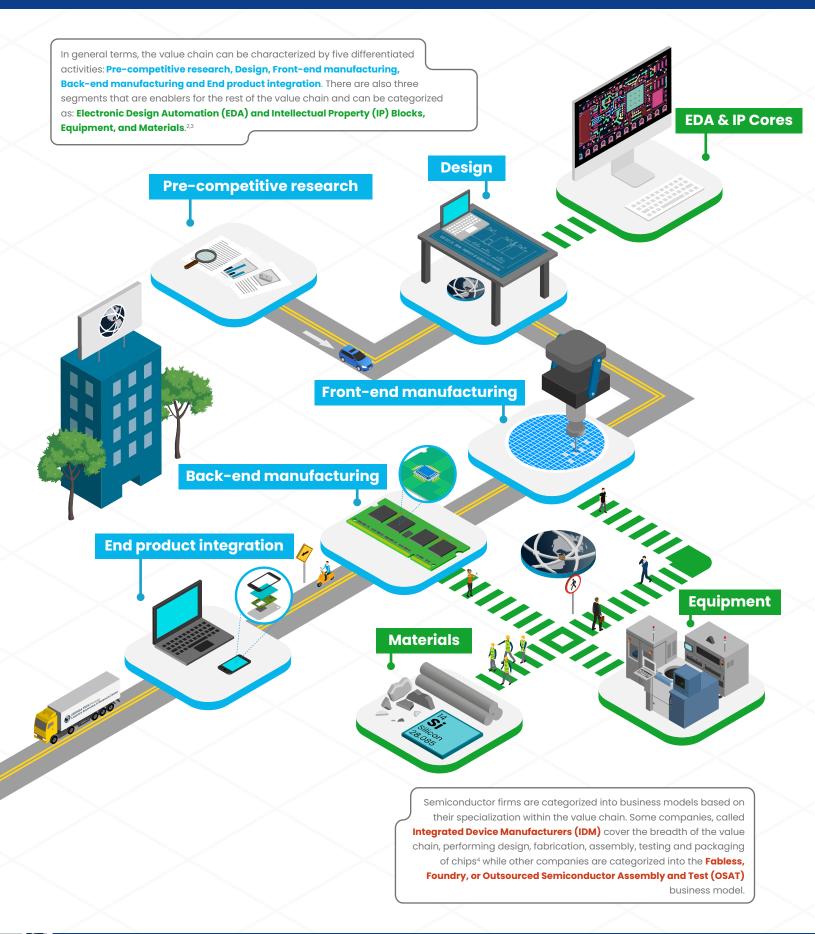

### **Exploring the Semiconductor Global Value Chain**

The semiconductor industry plays a vital role in today's global economy, as it supplies the specialized components that are crucial for the functioning of a wide range of electronic devices, making the industry an essential part of modern technology. From personal computers to smartphones, modern automobiles, and even washing machines, these components are essential to their functioning. This expanding sector is expected to have a pivotal role in shaping the course of cutting-edge technologies such as 5G, the Internet of Things, and Artificial Intelligence. Its rapid growth is anticipated to serve as an important driver for these advancements and beyond.1

To meet the demand and required scale for this technology, a highly specialized global supply chain has been developed over the past three decades, leveraging different regions' comparative advantages to optimize the design and manufacture of semiconductors. This structure has enabled continual cost savings, performance enhancements, and increasingly smaller chips, while providing end users with electronics at lower prices.

The semiconductor industry is experiencing a swift expansion, with the global value chain undergoing a significant transformation. This shift is being driven by a combination of factors, including the escalating geopolitical tensions between China and the United States, the COVID-19 pandemic-induced chip shortage, and other related developments. As a result, semiconductor companies are being forced to rethink their supply chains and explore new ways of doing business in order to remain competitive in an increasingly complex and uncertain global marketplace.

In this context, will explore the structure of the semiconductor global value chain, its main elements, the location of specialized activities and the potential role that Latin America and Panama could play in this global reconfiguration.

# Semiconductor Value Chain Structure

# Pre-competitive research

Pre-competitive research is dedicated to exploring the materials and chemical processes that have the potential to keep improving computing and power efficiency. By delving into these areas, researchers hope to gain a deeper understanding of the underlying principles that govern semiconductor technology.

This type of research is basic research, which means it is published, shared openly within the scientific community and is collaborative by nature<sup>5</sup>, in contrast to proprietary research and industrial development which is usually kept within the industry and company sphere. It is important to note that both types of research are complementary. For example, in the case of the U.S., federal government investment into basic research stimulated greater levels of private R&D investment.6

Typically, a worldwide group of scientists hailing from private corporations, universities, academic institutions, government-sponsored labs, and independent research institutions works together to conduct pre-competitive research. This collaboration helps to share the costs of research and prevent duplication of efforts.

Research in semiconductor processes and materials takes time, though. For example, research in the latest advancements in Extreme Ultra-Violet (EUV) lithography, which is critical for the fabrication of the most advanced chips being produced today, started in the mid-1980s with the earliest concepts building upon multilayer mirror research all the way to 2019 when the first EUV-enabled commercial product was released.7

Investment into research activities has led to positive virtuous cycles. For example, in the case of the U.S., despite the fact that federal government funding for basic research in this field has not experienced substantial growth in comparison to private sector investments, the country still leads the world in semiconductor R&D.<sup>5,8</sup> It has some of the most notable clusters of technical universities and semiconductor businesses in the world, which has led to a positive feedback loop of

learning, research, entrepreneurship, and financial access to support innovation.

Considering this reality, many players around the globe are focusing on research as well. China for example is seeking to heavily boost basic research, increasing government spending in this segment by 11% in 2021, as an effort to build a strong domestic semiconductor industry.<sup>2,9</sup>

According to analysis by Boston Consulting Group, pre-competitive research accounts for about 15 to 20% of the overall R&D investment across all sectors in most leading countries.<sup>2</sup>

# Vertically Integrated Business Model: Integrated Device Manufacturers (IDMs)

An integrated device manufacturer (IDM) is a semiconductor business model that creates, produces, and markets integrated circuits (ICs). A typical IDM has a fabrication facility where it manufactures its ICs and owns its own line of branded chips. This means that an IDM handles design, manufacturing of wafers, packaging, testing and assembly of chips.

Notable examples of IDMs include Intel, Infineon, Samsung, Micron, SK Hynix and Texas Instruments (TI). Samsung is an illustration of an IDM that furthermore offers foundry and design services to other semiconductor firms.<sup>10</sup>

# Design

Design is the process of producing an implementation ready to be laid out into a chip, onto a board, or a combination of both. Design involves creating the layout and functionality of a chip. This is done by designing the physical layout of the chip, determining the placement of components and creating the electrical connections between them.

Semiconductor design involves the careful consideration of a chip's architecture to optimize for specific parameters such as cost, power consumption, and capacity. These parameters are determined based on the unique needs of the chip in question. By carefully sketching out

the architecture, designers are able to ensure that the chip performs optimally and meets the desired specifications.<sup>12</sup>

Advanced electronic design automation (EDA) tools, reusable architectural building blocks (or "Intellectual Property (IP) cores") and, occasionally, outsourced chip design services from specialist technology vendors are used in the design process.

Semiconductors are extremely difficult to design and produce, requiring a significant amount of knowledge and skill. Because of this, the design process plays a significant role in contributing to the overall value of a semiconductor. BCG analysis has found that design work contributes around 53% of the total value added and 65% of all semiconductor industry R&D.<sup>2</sup>

Not only is the design process difficult, but also very expensive. With the increasing complexity of semiconductors, the expenses associated with their development have risen sharply. Although EDA tools play a crucial role in simulating, testing, and enhancing chip design<sup>13</sup>, the design process still requires significant labor, time, and cost. It takes a team of hundreds of engineers several years to develop current complex chips, such as the "system-on-chip" (SoC) processors that drive today's smartphones. This endeavor occasionally makes use of external IP and design support services.

The description of advancements in semiconductor manufacturing technology is commonly articulated by referencing **nodes**.<sup>14</sup> The term "node" originally referred to the size of transistor gates in electronic circuits, measured in nanometers. However, its meaning has evolved over time to encompass various circuit architectures and manufacturing technologies, as well as smaller features.

The expenses associated with designing chips are rising for each new technology node, with costs for advanced SoC reaching approximately US\$51 million for 28nm, US\$106 million for 16nm, US\$174 million for 10nm, US\$298 million for 7nm, and around US\$542 million for 5nm chips. 15 Accenture estimates that the expenses linked to the design process for cutting-edge 3nm nodes, as those for use in new generation

smartphones, can vary from US\$500M to more than US\$1.5B, which highlights the way costs have been explosively scaling for advanced chip design.3

The design phase is the most R&D-intensive stage in the value chain and serves as the primary facilitator of silicon technology. It is estimated that chip design constitutes approximately 53% of the industry R&D, 13% of the industry capital expenditure, and 50% of the value added.

#### Design layer specialization: Fabless firms

"Fabless" firms specialize in the design stage of the value chain structure. As their name implies, they do not take part in the fabrication stage of semiconductors, and are focused on the design and marketing of chips. These firms outsource fabrication, assembly, packaging and testing.16 The rise of fabless firms can be attributed primarily due to the challenges of managing the substantial costs for R&D that design requires as well as the capital intensity of manufacturing.

In general terms, most of what fabless firms concentrate on is the design of logic chips, due to the market's demand for enhanced power and performance capabilities which have accelerated in response to the rapid development cycles of smartphones and the emergence of cutting-edge applications in AI and high-performance computing.<sup>2</sup>

#### **Key players**

Among the major players in chip design are Qualcomm, Broadcom, NVIDIA, AMD, Xilinx, and Marvell from the U.S.; MediaTek, Novatek Microelectronics, and Realtek from Taiwan; and Huawei HiSilicon from China.17

The field of chip design has significant barriers of entry. However, hyperscalers, companies that operate massive data centers and cloud infrastructure, are now recognizing the immense value that can be derived from this stage of the value chain and are taking steps to establish their presence in this domain. Players such as Alibaba, Alphabet (Google), Amazon, Apple, Facebook, Microsoft, and Tesla are all designing their chips. The demand for application-specific chips

(ASIC) that excel in performing a single task, such as AI accelerators for training or inference, is one of the key drivers behind this trend.<sup>3,16</sup>

Geographically, most of the global semiconductor design is performed in the United States, South Korea, Japan, Taiwan, Europe, and China. The United States leads in design of logic and analog chips, South Korea in memory chips, and Europe in discrete chips. Although most of its chips cannot compete with state-of-the-art U.S. chips, China designs many logic chips, some discrete chips, and is also beginning to design memory chips.<sup>18</sup>

#### **EDA & IP Cores**

An **intellectual property core** (IP core) is a reusable unit of logic or integrated circuit (IC) layout design. We can think of them as standardized designs or "templates" for microprocessors and functionalities which can be reutilized in chip designs, for example in system-on-a-chip designs. These IP cores may be licensed to be used by others in their own ICs and semiconductors.<sup>20</sup>

EDA and the associated algorithms are fundamental for the design of chips, since they have tools that allow to simulate functionality, integrate IP cores, and verify designs. EDA now contains AI capabilities which allow it to design "floorplans" for microchips and offer the promise of better, more-rapidly produced chip designs.<sup>21</sup>

According to BCG, EDA and IP core vendors invest around 30-40% of their revenues into R&D and constitute approximately 4% of the value

added of the industry.

#### **Key players**

Among the major players in EDA are Cadence and Synopsis from the U.S. and Mentor Graphics, a U.S.-based subsidiary of the German firm Siemens. This has led to the world's leaders in EDA to be concentrated in the U.S. with a control of 70% of the global market for EDA tools.<sup>22</sup>

Key players in IP include ARM from Japan, and Cadence and Intel from the U.S. According to estimates from a Georgetown University CSET study, the United States and United Kingdom combined were responsible for over 90% of the core IP market in 2019.<sup>17</sup>

The same report states that even though China is lacking in core IP development, a series of acquisitions, joint ventures, and open-source development provide opportunities to increase its capabilities in this sector.

# Front-end Manufacturing: Fabrication

Front-end manufacturing refers to the initial stages of the production process where raw materials are processed and transformed into wafers and prepared for downstream manufacturing steps.<sup>23</sup>

Semiconductor fabrication facilities, commonly known as "fabs", utilize advanced technology to produce integrated circuits at the nanoscale level by fabricating the chip design onto silicon wafers. Numerous chips with the same design are present on each wafer.

The process of front-end manufacturing is a highly intricate and rigorous procedure that requires an exceptional degree of precision and accuracy to ensure the reliability and performance of the final product.

The manufacturing process commences with a cylindrical crystalline ingot that undergoes slicing, polishing, and patterning to produce thin wafers of varying diameters. Upon receiving a batch of wafers,

engineers in the fabrication plant employ a range of processes such as lithography, etching, implantation, planarization, passivation, and deposition.24

These techniques are used to construct over 60 layers of transistors, along with an interconnected network of wires to establish connections between the transistors. The system employs a diverse range of inputs, comprising unprocessed wafers, standardized chemicals, specialized chemicals, and various processing and testing apparatus and instruments, spanning multiple stages.3

The semiconductor wafer manufacturing process involves a range of 400 to 1400 steps, depending on the product in question. The process of wafer fabrication in a mature node can consist of up to 350 steps and take 45-60 days, while in an advanced node it can involve over 700 steps and take more than 60 days.<sup>25</sup>

Although silicon is the conventional material for semiconductor devices, other materials such as gallium arsenide, gallium nitride, silicon carbide and indium phosphide can be utilized based on the specific device being manufactured. Improvements in the quality and purity of materials have led to better performance and longer lifetimes in semiconductors. The increasing variety of end applications for semiconductors has led to a corresponding expansion of opportunities to leverage these non-silicon alternatives.<sup>26</sup>

#### Front-end Manufacturing is Capital Intensive

In general, the relationship between node size and chip power is directly related, as a smaller node size allows for a higher density of transistors to be integrated onto the same area, which translates to greater power efficiency, and faster performance.<sup>27</sup> This principle is based on "Moore's Law" and it is a crucial observation and projection within the semiconductor industry, which states that the number of transistors on an integrated circuit doubles every two years.<sup>28</sup>

The technological proficiency of a fabrication plant can be measured by the smallest size of transistors that can be produced by the plant's

production nodes, expressed in nanometers. That is, a 7nm fab can produce smaller transistors and denser chips than a 28nm fab.29 The nodes that are more advanced and smaller in size require higher capital expenditures for fabrication, similar as in the case of design.

The increasing progression of Moore's Law and the reduction in transistor size is leading to a significant rise in the complexity and cost of front-end manufacturing.

According to BCG, the capital expenditure required for a semiconductor fab of standard capacity ranges from approximately US\$5 billion for advanced analog fabs to US\$20 billion for advanced logic and memory fabs, which includes expenses for land, buildings, and equipment. That same report estimates that the capital expenditure allocated by companies that focus on semiconductor manufacturing usually constitutes 30-40% of their annual revenue and consequently, wafer fabrication constitutes around 65% of the overall industry capital expenditure and 25% of the value added.

#### Manufacturing layer specialization: Foundries

The foundry model is a business model which concentrates specifically on the manufacturing layer of the semiconductor value chain. In general terms foundries address the fabrication activities of fabless firms, and IDMs as well. This allows foundries to have a large customer base composed of both design firms like AMD and Nvidia, and IDMs like Intel. TSMC is a great example since they were one of the pioneers of the foundry business model, and today are one of the few foundries in the world that can produce chips with 5nm technology nodes.<sup>30</sup>

#### **Key players in the front-end** manufacturing industry

TSMC, UMC, SMIC, and GlobalFoundries are prominent semiconductor foundries that offer front-end manufacturing solutions. IDMs such as Intel, Samsung, Micron, NXP, Texas Instruments, and Infineon carry out in-house front-end manufacturing.

The majority of front-end manufacturing activities are concentrated in

East Asia, specifically in Taiwan, South Korea, and Japan. However, there are also some clusters of such activities in the United States and Europe.

# **Back-End Manufacturing**

Wafers manufactured by the semiconductor fabrication facilities are processed through back-end manufacturing activities to produce finalized chips that are suitable for integration into electronic devices. This stage is composed of the assembly, packaging and testing processes (APT).

At this stage, companies engage in the process of dicing silicon wafers into discrete chips. To ensure that each chip meets the required quality standards, wafers are tested before they are sliced and packaged. In wafer tests, the properties and qualities of the numerous chips that are on a wafer are inspected.

Preventing the distribution of faulty products is one of the key goals of semiconductor testing. To ensure the quality and dependability of the products, a thorough inspection process that incorporates several forms of testing is required. However, these lengthy procedures increase the amount of time spent testing, as well as the amount of equipment, labor, and production expenses.<sup>31</sup> This has led back-end manufacturing activities to be labor intensive with typically lower profit margins when compared to front-end manufacturing.<sup>32</sup>

After the wafers are tested and diced, semiconductor chips undergo packaging, which is designed to protect the semiconductor, by being embedded within safeguarding frames and subsequently encapsulated in a resinous shell.<sup>33</sup> This is done through an electrical packaging process so that the chip can be molded into the appropriate design and form.<sup>34</sup>

After this process, packaged chips are transported to assemblers who are responsible for putting together the chips into circuit boards. These circuit boards are equipped with passive components and protective encasing to ensure their durability and longevity.

The chips undergo additional rigorous testing procedures under various conditions of voltage, electrical signals, and temperature prior to their shipment to manufacturers of electronic devices.

APT, in general terms, involves fewer sophisticated processes and equipment, a lower capital investment and higher labor when compared to wafer manufacturing.<sup>17</sup> However, innovations in packaging and the successive shrinking of transistor size are changing this dynamic.

A report by BCG states that companies that focus on back-end manufacturing activities generally allocate more than 15% of their yearly revenue towards capital expenditure for facilities and equipment.<sup>2</sup> The same report estimates that in 2019, back-end manufacturing activities constituted 13% of the industry's total capital expenditure and contributed 6% to the industry's overall value added.

#### **APT layer specialization:**

#### **Outsourced Semiconductor Assembly And Test** (OSAT)

Outsourced Semiconductor Assembly and Test (OSAT) are companies that offer third-party integrated circuit assembly, packaging and testing services. OSAT companies are contracted by fabless firms like AMD and Nvidia, or by IDMs like Intel.

There are many businesses contending for the top slots in the OSAT market. China is currently an emerging market for OSAT providers mainly because, in accordance with their "Made in China 2025" goal, the local government provides incentives and assistance for regional OSAT operators.35

Like other segments of the semiconductor industry, OSAT providers are grappling with escalating costs. This has prompted several semiconductor companies to adopt an in-house approach to packaging, assembly, and testing to mitigate expenses and alleviate supply chain constraints.

#### The APT global landscape.

The OSAT market grew from \$17 billion in 2009 to more than \$30 billion in 2019<sup>17</sup> and it is projected to reach \$60.3 billion by 2031, which indicates its growth potential alongside the rest of the semiconductor value chain.<sup>36</sup> In contrast to advanced wafer manufacturing which ranges in the billions of dollars for setting up a manufacturing plant, setting up an advanced packaging manufacturing line for an OSAT cost \$100 million to \$200 million in 2019.37

The geographical distribution of back-end manufacturing has predominantly gravitated towards Asia due to the substantial labor-intensive nature of these processes. This trend can be attributed to the comparatively lower wages prevalent in the region. In 2021, the United States accounted for a mere 5% of the global APT capacity, with a significant portion being concentrated in China (38%), Taiwan (19%), and South Korea (9%).38 Additionally, according to the Worldwide Assembly & Test Facility Database published by SEMI and TechSearch, in 2021 there were 373 OSAT facilities globally, of which 111 were located in China, 107 in Taiwan, 45 in Southeast Asia, 23 in Japan, while 46 were in the Americas and 20 in Europe.<sup>39</sup> It is significant to note that APT capacity does not directly correlate with OSAT market share, but it does provide insights to the spatial distribution of back-end manufacturing activities.

This concentration of OSATs in Asia is seen also in the outsourcing practices of leading chip producers. For example, Texas Instruments which is a U.S.-based IDM doesn't have any APT facility in the U.S. and outsources its packaging processes to other countries. Intel is also dependent on Asia for its APT processes and it is estimated that both Texas Instruments and Intel perform about 30% of their packaging in China and Taiwan.40

#### **Key players**

The key players in assembly, testing and packaging include ASE Group and Powertech Technology from Taiwan, Amkor Technologies from the United States and JCET, Tongfu Microelectronics, and Tianshui Huatian

Technology from China.

Just as in other areas of the semiconductor value chain, the OSAT market has undergone significant consolidation. In 2019 the 20 largest OSAT companies held 92% of the back-end market, with Taiwanese OSATs accounting for 53% of the share, and ASE Group was the firm with the largest share at 26%.17

The rest of the global OSAT market is held by China (21% market share) and other cost-advantageous locations. Facilities are also being built in Malaysia, Vietnam and the Philippines.<sup>17</sup>

# **Equipment**

Semiconductor manufacturing relies on a variety of sophisticated equipment provided by specialist vendors. These equipment types, including lithography tools, metrology, and inspection equipment, drive the capital expenditures of fabrication players. Lithography tools, particularly those utilizing Extreme Ultra-Violet (EUV) technology, are crucial for producing advanced chips at 7 nanometers and below, with a single EUV machine costing \$150 million. Metrology and inspection equipment are essential for managing the manufacturing process and ensuring high yields.

Semiconductor equipment can be categorized into wafer fabrication and processing equipment, test equipment, and assembly/packaging equipment. The average cost of each piece of equipment is in the range of \$2 million to \$6 million.

#### **Key players**

Key players in equipment include Applied Materials, Lam Research, and KLA in the United States, ASML in the Netherlands, and Tokyo Electron in Japan. Even though the equipment vendors offer a variety of equipment types, each player specializes in specific steps in the fabrication process.17

BCG reports that developing and fabricating such advanced equipment requires significant investments in research and

development (R&D), typically accounting for 10% to 15% of revenues for semiconductor manufacturing equipment companies. These firms contributed 9% of the industry's R&D and 11% of its value added in 2019.

#### **Materials**

Semiconductor fabrication also heavily relies on specialized suppliers of materials, which are integral to various processes such as patterning, deposition, etching, polishing, equipment operations, facility cleaning, and packaging. These materials include chemicals, gases, minerals, and high-purity materials. Some examples include minerals such as raw polysilicon, chemicals such as hydrogen fluoride and nitric acid, and gases such as neon and helium.<sup>41</sup>

The number and amount of specialized process chemicals used in wafer fabrication continue to rise as semiconductors become more complex. Additionally, the miniaturization of semiconductors necessitates the development of new materials to connect transistors. While back-end materials have lower technical barriers compared to front-end materials, they still require specialized production facilities with significant investments.

#### **Key players**

Key players in the semiconductor materials industry include Shin-Etsu Chemical Co., Sumitomo Chemicals, and Mitsui Chemicals from Japan; BASF, Linde, Merck KGaA from Europe; Taiwan Specialty Chemicals Corporation from Taiwan; and Dow Chemical and DuPont from the US.<sup>3</sup>

These materials suppliers not only serve the semiconductor industry but also cater to other industries like pharmaceuticals, industrial, and agriculture. This diversification makes the materials stage of the value chain less susceptible to shocks in the semiconductor industry.

Production of these highly specialized materials requires significant investments, and annual capital expenditure by leading global suppliers can range from 13% to 20% of their revenues. Materials suppliers contributed 6% of the industry's total capital expenditure and accounted for 5% of its value added in 2019.

# **End-product integration**

End-product integration is the process of designing and delivering complete products to consumers, incorporating various components and technologies to meet specific needs. In the semiconductor value chain, this involves the collaboration of Original Equipment Manufacturers (OEMs) and Electronics Manufacturing Services (EMS) providers.

OEMs are companies that design and deliver final products to consumers. They leverage their in-house engineering capabilities to create products that cater to market dynamics and consumer preferences. While they traditionally focused on hardware like computers and phones, OEMs now offer a wide range of products, from smart watches to industrial robots.

Semiconductor OEMs design these products and source chips from Integrated Device Manufacturers (IDMs) or fabless companies. Major OEMs are also developing their own design capabilities and outsourcing manufacturing to foundries. They often collaborate with EMS partners for packaging and assembly.

EMS providers play a crucial role by offering services beyond manufacturing. They handle tasks such as demand forecasting, supplier management, inventory, logistics, delivery, repair, and customer service. This allows OEMs to scale up their production, customize products, reduce time to market, and achieve supply chain efficiencies. EMS providers are concentrated in Asia due to lower costs, but they establish production sites worldwide to be closer to OEMs' end-consumer markets.

#### **Key players**

Key players in OEM include Apple, Samsung, Huawei, Lenovo, Dell, and HP. In EMS, notable players are Foxconn, Jabil, and Flex. Foxconn has achieved significant scale and is expanding into upstream stages of the value chain, including semiconductor manufacturing and strategic partnerships.

# **Building a stronger supply chain** through diversification

The rapid growth of the semiconductor market, driven by increased consumption of end products and the demand of chips with higher performance capabilities, presents an increased opportunity for the relocation of value chain activities to Latin America.

However, the reshaping of the global semiconductor value chain is riddled with complexity. The capital intensity of front-end manufacturing, which constitutes nearly two thirds of overall industry capital expenditure, presents a barrier to the relocation or expansion of manufacturing capacity into the region, both for foundries and IDMs.

There is a move visible opportunity for Latin America in general, and Panama in particular, in back-end manufacturing -assembly, packaging and testing processes—due to the lower capital investment involved, lower sophistication in terms of equipment and processes, and higher labor intensity. These attributes make the APT layer, coupled with distribution activities, a more natural fit for geographic diversification. The relatively higher labor intensity entails that new sites need a strong labor pool that can absorb the demands of an APT facility. There's already APT capacity deployed in some

countries in the region, and the growing consumer market for goods requiring electronic components in the region signals a potential for further growth beyond current capabilities.

Geographic diversification of back-end manufacturing capacity also requires improved reliability of the supporting logistics platform, to ensure the efficient flow of goods between front-end and back-end manufacturing facilities, as well as complementary process inputs required in each site, both for OSATs and IDMs. Enhanced regional distribution systems may have an added strategic value for IDMs, as they may leverage existing localized logistics capacity associated to their end-product network to serve other tiers in the value chain. OSATs also stand to gain from regional logistics capabilities built near back-end manufacturing sites by decreasing supply risk associated to

their operation, while also gaining proximity to OEM and EMS sites in the region.

Strategic inventory positioning in the region can be a powerful tool in a high-value segment such as semiconductors. The high level of integration within the Panama intermodal cluster, and the strong inbound and outbound connectivity available at that site, serves as an example of logistics capabilities available within Latin America that can serve the semiconductor global value chain and provide a platform for the growth of that industry.

There are great opportunities for the development of some facets of semiconductor manufacturing in Latin America, and the region as a whole should anchor its role in this industry on its existing strengths, to truly respond to the needs of a complex and rapidly growing market. The semiconductor industry can be a vital component in boosting regional economic growth, but this may only be achieved through targeted strategies for optimizing value generation for supply chain stakeholders.

#### **Notes**

- Cameron, L. (2019, December 19). As 5G Approaches, Semiconductor Industry Must Combat

Friction Points to Make World of 'Smart Everything' a Reality. IEEE Computer Society.

https://www.computer.org/publications/tech-news/trends/5G-semiconductor-industry-drives-smart-everything-iot/

- 2. Varas, A., Varadarajan, R., Goodrich, J., & Yinug, F. (2021). Strengthening the global semiconductor supply chain in an uncertain era. Boston Consulting Group and Semiconductor Industry Association.

- Alam, Chu, Krishnan, Leblanc, Alsheik, Chen, Kurniawan, & Nandanampati. (2022, February 1).

The Power of the Semiconductor Value Chain | Accenture. The Power of the Semiconductor Value Chain | Accenture. Retrieved January 10, 2023, from https://www.accenture.-com/us-en/insights/high-tech/semi-value-chain

- [Semiconductor Glossary] Integrated Device Manufacturer (IDM). (n.d.). Samsung Semiconductor Global. Retrieved June 30, 2023, from https://semiconductor.samsung.com/support/tools-resources/dictionary/semiconductor-glossary-integrated-device-manufacturer-idm

- Institute of Medicine (US). (2010, January 1). Types of Precompetitive Collaborations Extending the Spectrum of Precompetitive Collaboration in Oncology Research NCBI Bookshelf. NIH National Library of Science. Retrieved June 5, 2023, from https://www.ncbi.nlm.nih.gov/-books/NBK210028/

- 6. Nathan Associates. (2020, June). Sparking Innovation. Semiconductor Industry Association. Retrieved June 27, 2023, from https://www.semiconductors.org/sparking-innovation/

- 7. Making EUV: from lab to fab. (2022, February 16). Making EUV: From Lab to Fab Stories | ASML. https://www.asml.com/en/news/stories/2022/making-euv-lab-to-fab

- Freeman, D. (2022, May 17). Where Does the U.S. Stand on Semiconductor R&D? 3D InCites.

3D InCites. https://www.3dincites.com/2022/05/whe-re-does-the-u-s-stand-on-semiconductor-rd/

- 9. China's attempts of self-sufficiency in the semiconductor supply line The Foundation For Future Supply Chain | FFSC. (2022, February 16). The Foundation for Future Supply Chain | FFSC. https://futuresupplychains.org/chinas-semiconductor-supply-line/

- Integrated Device Manufacturer (IDM). (n.d.). Semiconductor Engineering. Retrieved July 21, 2023, from https://semiengineering.com/knowledge\_centers/manufacturing/integrated-device-manufacturer-idm

- Semiconductor Engineering Knowledge Center. (n.d.). Chip Design. Semiconductor Engineering. Retrieved June 22, 2023, from https://semiengineering.com/knowledge\_centers/eda-design/definitions/chip-design/

- 12. Thadani, A., & Allen, G. C. (2023, May). Mapping the Semiconductor Supply Chain: The Critical Role of the Indo-Pacific Region. Mapping the Semiconductor Supply Chain: The Critical Role of the Indo-Pacific Region. Retrieved June 23, 2023, from https://www.csis.org/analysis/mapping-semiconductor-supply-chain-critical-role-indo-pacific-region

- 13. System-on-Chip (SoC) Design Elements Guide | Synopsys Cloud. (n.d.). System-on-Chip (SoC) Design Elements Guide | Synopsys Cloud. https://www.synopsys.com/cloud/insights/system-on-chip-design.html

- 14. Semiconductor Engineering. (n.d.). Nodes. Retrieved June 28, 2023, from https://semiengineering.com/knowledge\_centers/manufacturing/process/nodes/

- 15. Shilov, A. (2023). Synopsys Intros Al-Powered EDA Suite to Accelerate Chip Design and Cut Costs. Synopsys Intros Al-Powered EDA Suite to Accelerate Chip Design and Cut Costs. Retrieved June 28, 2023, from https://www.anandtech.com/show/18798/synopsysai-aipowered-eda-suite-accelerates-chip-design-and-cuts-costs-

- 16. What is a Fabless Company AnySilicon. (2019, January 2). AnySilicon. https://anysilicon.-com/what-is-a-fabless-company/

- 17. Kleinhans, J. P., & Baisakova, N. (2020). The global semiconductor value chain: A technology primer for policy makers. Stiftung Neue Verantwortung, 1-30.

- 18. Khan, S. M., Mann, A., & Peterson, D. (2021). The semiconductor supply chain: Assessing national competitiveness. Center for Security and Emerging Technology, 8(8).

- 19. Maxfield, C. (2003). Bebop to the Boolean Boogie: An Unconventional Guide to Electronics Fundamentals, Components, and Processes. Newnes.

- 20. Awati. (2022, November). What is an intellectual property core (IP core)? -- TechTarget Definition. TechTarget. Retrieved June 29, 2023, from https://www.techtarget.com/whatis/definition/IP-core-intellectual-property-core

- 21. Kahng, A. B. (2021, June 9). Al system outperforms humans in designing floorplans for microchips. Nature. https://doi.org/10.1038/d41586-021-01515-9

- 22. Yang. (2022, August 18). Inside the software that will become the next battle front in US-China chip war. MIT Technology Review. Retrieved June 29, 2023, from https://www.technologyreview.com/2022/08/18/1058116/eda-software-us-china-chip-war/

- 23. Frontend Electronics Manufacturing: Processes, Challenges, and Improvements. (2020, April 16). Frontend Electronics Manufacturing: Processes, Challenges, and Improvements | Advanced PCB Design Bl. https://resources.pcb.cadence.com/blog/2020-frontend-electronics-manufacturing-processes-challenges-and-improvements

- 24. Samsung Tech Blog. (2022, November 28). A short introduction to semiconductor fabrication | Samsung Semiconductor EMEA. Samsung Semiconductor EMEA. Retrieved June 30, 2023, from https://semiconductor.samsung.com/emea/news-events/tech-blog/a-short-introduction-to-semiconductor-fabrication

- 25. Why the global chip shortage is making it so hard to buy a PS5. (2021, August 31). Why The Global Chip Shortage Is Making It so Hard to Buy a PS5 the Verge. https://www.theverge.-com/2021/8/31/22648372/willy-shih-chip-shortage-tsmc-samsung-ps5-decoder-interview

- 26. Hart. (2023, February 15). Semiconductor Manufacturing Process: How are semiconductor chips made? MRL. Retrieved June 30, 2023, from https://www.mrlcg.com/latest-media/semi-conductor-manufacturing-process-how-are-semiconductor-chips-made-299611/

- 27. Arslan. (2022, March 7). What Does nm Mean For CPUs? How Does It Make a Difference? MUO: Make Use Of. Retrieved June 30, 2023, from https://www.makeuseof.-com/what-does-nm-mean-cpu-does-it-make-difference/

- 28. Roser, Ritchie, & Mathieu. (2023, March 28). What is Moore's Law? Our World in Data. Retrieved June 30, 2023, from https://ourworldindata.org/moores-law

- 29. Hruska. (2021, February 12). How Are Process Nodes Defined? ExtremeTech. Retrieved June 26, 2023, from https://www.extremetech.com/computing/296154-how-are-process-nodes-defined

- 30. Liu, M. (2021, May 14). Taiwan and the foundry model Nature Electronics. Nature. https://-doi.org/10.1038/s41928-021-00576-y

- 31. SK Hynix Newsroom. (2023, April 6). Semiconductor Back-End Process Episode 1: Understanding Semiconductor Testing. Retrieved July 24, 2023, from https://news.skhynix.com/semiconductor-back-end-process-episode-1-understanding-semiconductor-testing/

- 32. Alexander, Michael. 2019. How OSAT companies can improve their profitability in a low-margin environment. https://www.rolandberger.com/nl/Point-of-View/Be-tween-a-rock-and-a-hard-place-OSATcompanies-need-a-new-playbook.html

- 33. A Guide to Outsourced Semiconductor Assembly and Test. (n.d.). Wafer World. Retrieved July 4, 2023, from https://www.waferworld.com/post/guide-to-outsourced-semiconductor-assembly-and-test

- 34. Eight Major Steps to Semiconductor Fabrication, Part 9: Packaging and Package Testing. (2015, June 17). Samsung Newsroom. Retrieved July 21, 2023, from https://news.samsung.com/-global/eight-major-steps-to-semicon-ductor-fabrication-part-9-packaging-and-package-testing

- 35. OSAT Outsourced Semiconductor Assembly and Test AnySilicon. (2021, June 3). AnySilicon. https://anysilicon.com/osat-outsourced-semiconductor-assembly-and-test/

- 36. Tejas, & Vineet. (2022, September). Outsourced Semiconductor Assembly and Testing Market 2031. Allied Market Research. Retrieved July 25, 2023, from https://www.alliedmarketresearch.com/outsourced-semiconductor-assembly-and-test-market-A08874

- 37. LaPedus. (2018, January 8). Packaging Challenges For 2018. Semiconductor Engineering. Retrieved July 25, 2023, from https://semiengineering.com/packaging-challenges-for-2018/

- 38. Arizona Commerce Authority & Boston Consulting Group. (2022, December 8). The National Semiconductor Economic Roadmap. Arizona Commerce Authority. Retrieved July 21, 2023, from https://www.azcommerce.com/national-semiconductor-economic-roadmap/

- 39. Worldwide Semiconductor Assembly and Test Facility Database now Tracks Integrated Device Manufacturers, 475 Facilities. (2022, February 23). SEMI. Retrieved July 21, 2023, from https://www.semi.org/en/news-media-press-releases/se-mi-press-releases/worldwide-semiconductor-assembly-and-test-facility-database-now-tr acks-integrated-device-manufacturers-475-facilities

- 40. Tomoshige. (2022, November 7). CHIPS+ and Semiconductor Packaging | Perspectives on Innovation | CSIS. CSIS Center for Strategic and International Studies. Retrieved July 21, 2023, from https://www.csis.org/blogs/perspectives-innovation/-chips-and-semiconductor-packaging

- 41. Singh, Sargent, & Sutter. (2023, April 19). Semiconductors and the Semiconductor Industry. In Federation of American Scientists. Congressional Research Service. Retrieved July 21, 2023, from https://sgp.fas.org/crs/misc/R47508.pdf

# About the Why Panama Program

In the current dynamic global landscape, it is clear that having access to high-quality insights is crucial when determining the optimal location for regional distribution in order to take advantage of the present structure of global value chains.

Georgia Tech Panama Logistics Innovation & Research Center recognizes the importance of key insights in the decision-making process, and works closely with companies seeking to assess their supply chains and how Panama can become a key part of their global logistics network.

The "Why Panama" program utilizes quantitative data and analytics to assess key variables and compare the costs, investments, and service benefits of setting up a distribution center in Panama. By conducting a thorough analysis, the program aims to provide businesses with valuable insights into the advantages of establishing a hub in Panama.

To know more you can contact Jeancarlos Chen at jeancarlos.chen@gatech.pa or Jorge Barnett at jorge.barnett@gatech.pa

#### **About Us**

The Georgia Tech Panama Logistics Innovation and Research Center is located in Panama City, Panama. It was launched in 2010 by an agreement between the Georgia Institute of Technology and the Government of Panama through the National Secretariat of Science, Technology and Innovation (SENACYT).

Reach us at www.gatech.pa

#### **CONTÁCTANOS**

(+507) 395-3030

georgiatechpanama@gatech.pa

in 🚹 💢 gatechpanama